# Improving Embedded Software with Data Science

Niklas Hauser

DLR Erfahrungsaustausch 2018

According to my parents I study something with computers.

But I also build autonomous robots in my spare time.

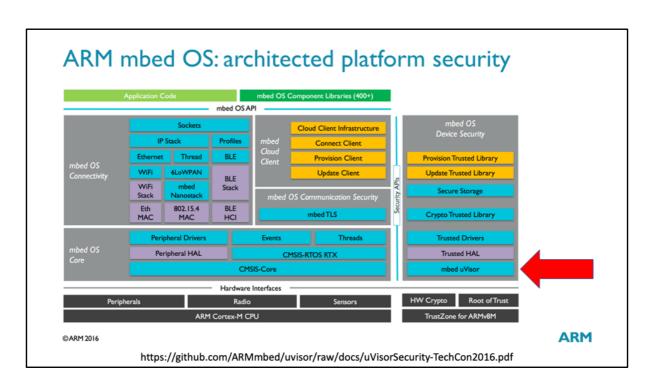

2.5y ago, I got hired by ARM to work on mbed OS Security, specifically uVisor.I spent almost 2y on the lowest levels of the ARMv7-M and ARMv8-M architectures.I've seen ALL the dirt of Cortex-M and I still (mostly) love it.

Then I quit work to hack on the largest research model railway in Germany. YOLO.

This is an introduction talk, so I'll keep the technical details light and mostly talk about concepts and ideas.

EMBEDDED: For the purpose of this talk I mean MICROCONTROLLERS, specifically AVR and ARM Cortex-M.

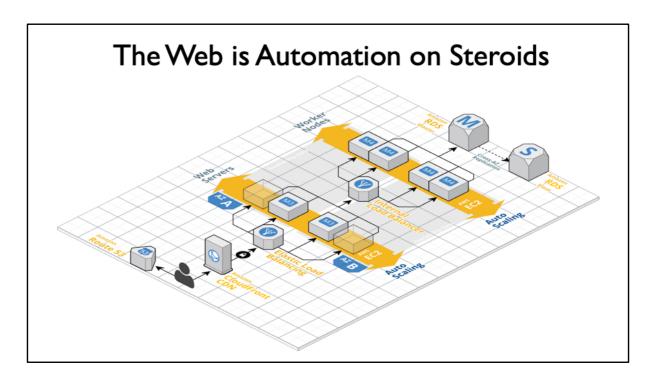

There many types of automation.

It evolved from a pure mechanization of labor to globe-spanning just-in-time industries.

This massive complexity only scaled with the introduction of computers.

The Web is the largest Automaton we've ever built! Everything you know about industrial automation, the Web does at >10x scale.

The key here is an asymmetry of effort: The developer configures the automation once, and then it just works<sup>™</sup>.

What similar technology can I use for embedded software to get similar scaling benefits?

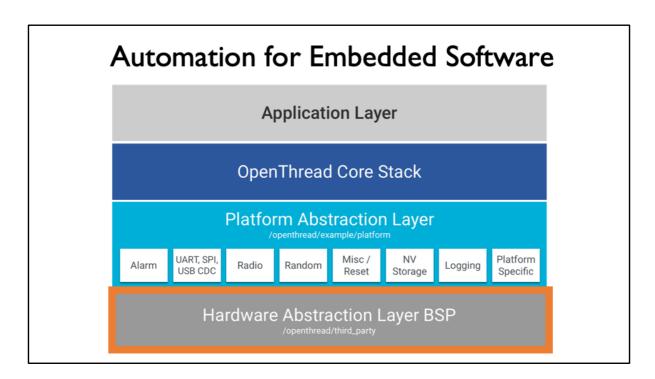

What needs to be scaled in embedded software? PORTING

HALs are usually provided by the vendor, to abstract hardware differences between devices.

USUALLY CODED BY HAND!

This is an insane BOTTLENECK.

PAL = Problem Anderer Leute

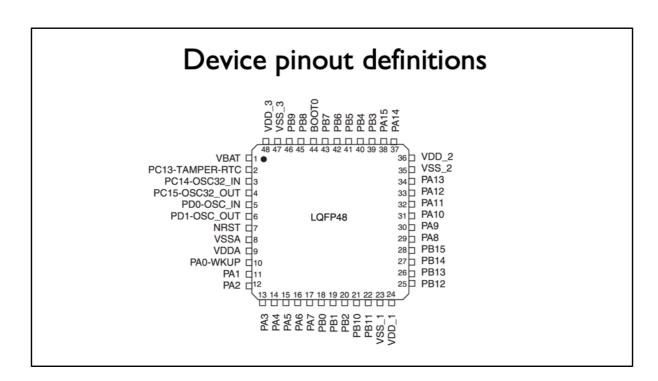

A typical abstraction of the HAL is to provide functions to access PINS. A single device can be packages in different ways, so the pins may differ.

### Mbed OS is ported manually (!) // TIM4 cannot be used because already used by the us\_ticker 86 87 MBED\_WEAK const PinMap PinMap\_PWM[] = { 88 {PA\_1, PWM\_2, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 2, 0)}, // TIM2\_CH2 - Default {PA\_2, PWM\_2, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 3, 0)}, // TIM2\_CH3 - Default (warning: not connected 89 {PA\_3, PWM\_2, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 4, 0)}, // TIM2\_CH4 - Default (warning: not connected 90 91 {PA\_6, PWM\_3, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 1, 0)}, // TIM3\_CH1 - Default {PA\_7, PWM\_3, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 2, 0)}, // TIM3\_CH2 - Default 92 93 // {PA\_7, FWM\_1, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 6, 1, 1)}, // TIM1\_CH1N - GPI0\_PartialRemap\_TIM1 {PA\_8, PWM\_1, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 1, 0)}, // TIM1\_CH1 - Default 94 95 {PA\_9, PWM\_1, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPIO\_PULLUP, 0, 2, 0)}, // TIM1\_CH2 - Default {PA\_10, PWM\_1, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 3, 0)}, // TIM1\_CH3 - Default 96 97 {PA\_11, PWM\_1, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPIO\_PULLUP, 0, 4, 0)}, // TIM1\_CH4 - Default 98 {PA\_15, PWM\_2, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 8, 1, 0)}, // TIM2\_CH1\_ETR - GPI0\_FullRemap\_TIM2 90 {PB\_0, PWM\_3, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 3, 0)}, // TIM3\_CH3 - Default 100 101 // {PB\_0, PWM\_1, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 6, 2, 1)}, // TIM1\_CH2N - GPI0\_PartialRemap\_TIM1 {PB\_1, PWM\_3, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 4, 0)}, // TIM3\_CH4 - Default 102 103 // {PB\_1, PWM\_1, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 6, 3, 1)}, // TIM1\_CH3N - GPI0\_PartialRemap\_TIM1 {PB\_3, PWM\_2, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 8, 2, 0)}, // TIM2\_CH2 - GPI0\_FullRemap\_TIM2 104 105 {PB\_4, PWM\_3, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 7, 1, 0)}, // TIM3\_CH1 - GPI0\_PartialRemap\_TIM3 {PB\_5, PWM\_3, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 7, 2, 0)}, // TIM3\_CH2 - GPI0\_PartialRemap\_TIM3 106 107 // {PB\_6, PWM\_4, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 1, 0)}, // TIM4\_CH1 - Default (used by ticker) // {PB\_7, PWM\_4, STM\_PIN\_DATA\_EXT(STM\_MODE\_AF\_PP, GPI0\_PULLUP, 0, 2, 0)}, // TIM4\_CH2 - Default (used by ticker) 108

In mbed OS this table describes the pin signal connections to the internal peripherals. You can see some manually commented out lines.

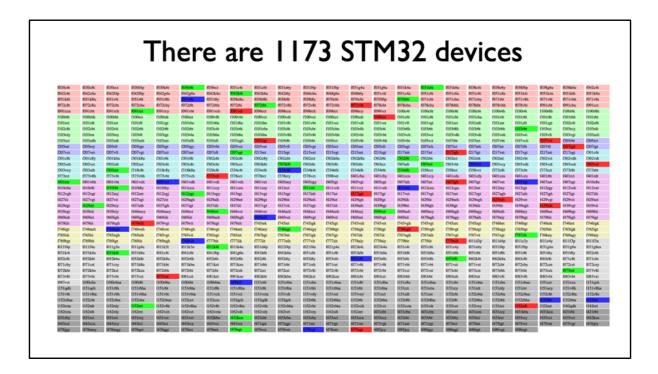

ST has 4-6 full-time engineers just for porting Mbed OS to STM32. They do it completely by hand.

ST adds new devices every couple of months.

Most of them differ in memory size, package and peripherals.

### Mbed OS supports 55 STM32 devices

\$ find targets/TARGET\_STM -name "PeripheralPins.c" targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/PeripheralPins.c targets /TARGET STM/TARGET STM32F0/TARGET NUCLED F030R8/ParinharalPine ( targe \$ find . -name "STM32\*.ld" targe /targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/TOOLCHAIN\_GCC\_ARM/STM32F0xx.ld targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_GCC\_ARM/STM32F0xx.ld

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLEO\_F030R8/device/T00LCHAIN\_GCC\_ARM/STM32F030X8.ld

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_ARM\_MICRO/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_ARM\_MICRO/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_ARM\_MICRO/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_ARM\_MICRO/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_ARM\_STD/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_ARM\_STD/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_GCC\_ARM/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_GCC\_ARM/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_GCC\_ARM/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_GCC\_ARM/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_DISCO\_F051R8/device/T00LCHAIN\_GCC\_ARM/startup\_stm32f05

targe:/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F0/TARGET\_STM32F targe./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLE0\_F030R8/device/TOOLCHAIN\_ARM\_MICR0/startup\_stm32 targe./targe./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLE0\_F030R8/device/TOOLCHAIN\_ARM\_STD/startup\_stm32f0 targe./targe./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLEO\_F030R8/device/TOOLCHAIN\_GCC\_ARM/startup\_stm32f targe./targe./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLE0\_F030R8/device/T00LCHAIN\_IAR/startup\_stm32f030x8 targe./targe./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLE0\_F031K6/device/T00LCHAIN\_ARM\_MICR0/startup\_stm32 targe./targe./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLEO\_F031K6/device/T00LCHAIN\_ARM\_STD/startup\_stm32f0 targe./targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe/targe targe./targe./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLEO\_F031K6/device/T00LCHAIN\_IAR/startup\_stm32f031x targe./targe./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLEO\_F042K6/device/TOOLCHAIN\_ARM\_MICRO/startup\_stm32 targe./targe./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLE0\_F042K6/device/T00LCHAIN\_ARM\_STD/startup\_stm32f0 targe./targe /targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLEO\_F042K6/device/T00LCHAIN\_GCC\_ARM/startup\_stm32f0

targe /targe /target/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLEO\_F042K6/device/T00LCHAIN\_GCC\_ARM/startup\_stm32f0 targe./targe

/targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLEO\_F042K6/device/T00LCHAIN\_GCC\_AKM/startup\_stm32f042x6

targe./targe /targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLEO\_F042K6/device/T00LCHAIN\_IAR/startup\_stm32f042x6 ./targets/TARGET\_STM/TARGET\_STM32F0/TARGET\_NUCLE0\_F070RB/device/T00LCHAIN\_ARM\_MICR0/startup\_stm32

- 55 manually created versions of the pinout data

- 51 Linkerscripts (some manually patched)

- ~200 startup scripts (some manually patched)

- We needed to modify the linker- and startup script for uVisor

X Billion IoT devices by 2035? HOW ARE YOU GOING TO MAINTAIN THIS?!?

Let's think about this problem in a calm and structured manner. Tea?

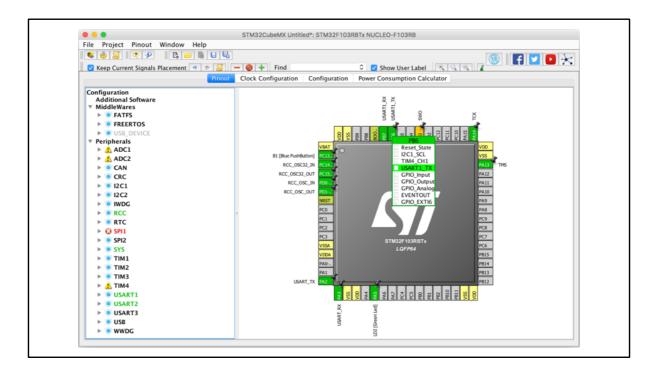

STMicro publishes a GUI App to initialize your STM32.

It's pretty good, the usability of this is great, you can just visually configure all your pins.

Understand conflicts between peripheral signal connections etc.

But I got curious, how does this work? It's backed by a lot of DATA!

| STM327103V8-80%xml       STM327103V8-80%xml       STM327103V8-7-60%xml       STM327103V8-7-60%xml         STM327103V8-6-70%xml       STM327103V8-7-67%xml       STM327103V8-70%xml       STM327103V8-70%xml         STM32710105-80%xml       STM327103V8-70%xml       STM327103V8-70%xml       STM327103V8-70%xml         STM32710105-70%xml       STM327103V8-70%xml       STM327103V8-70%xml       STM327103V8-70%xml         STM32710105-70%xml       STM32710105-70%xml       STM32710105-70%xml       STM32710105-70%xml         STM32710105-70%xml       STM32710105-70%xml       STM32710705-70%xml       STM32710105-70%xml         STM32710105-70%xml       STM32710105-70%xml       STM32710705-70%xml       STM32710705-70%xml         STM32710105-70%xml       STM32710706-70%xml       STM32710706-70%xml       STM32710706-70%xml         STM327107070-70%xml       STM32710706-70%xml       STM32710706-70%xml       STM32710706-70%xml         STM327107070-70%xml       STM32710706-70%xml       STM32710706-70%xml       STM32710706-70%xml         STM327107070-70%xml       STM32710706-70%xml       STM32710706- | ce Files |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

70MB of XML files, with a lot of device details.

- CPU: Type and Interrupt Vector Table

- Memories: Flash, RAM, Backup

- Peripherals: Type and Instances

- Gpio: Name and Signals

The reality is a bit more involved.

| ~                                                                | 200 STM3                                                                     | 32s +                                        | ~ <b>200</b> A                              | VRs                                                                                             |

|------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------|

| 📮 modm-io / <b>modm-d</b>                                        | evices                                                                       |                                              | ⊙ Unwatch - 5                               | tunstar 7 ∛Fork 1                                                                               |

| <> Code (1) Issues (0)                                           | 아 Pull requests 이 네 In                                                       | sights 🔅 Settings                            |                                             |                                                                                                 |

|                                                                  | all AVR and STM32 devices ht<br>nicrocontroller device-tree mod              | ttp://blog.salkinium.com<br>dm Manage topics | n/modm-devices                              | Edit                                                                                            |

|                                                                  |                                                                              |                                              |                                             |                                                                                                 |

| 74 commits                                                       | β <b>3</b> branches                                                          | ♥ 0 releases                                 | 2 contributors                              | ಫೆ MPL-2.0                                                                                      |

|                                                                  | ₽ 3 branches                                                                 | ♡ O releases                                 | 2 contributors Create new file Upload files | 화 MPL-2.0<br>Find file Clone or download ◄                                                      |

| Branch: develop - New p                                          | 0                                                                            | ♥ 0 releases                                 | Create new file Upload files                |                                                                                                 |

| Branch: develop - New p                                          | puli request                                                                 |                                              | Create new file Upload files                | Find file Cione or download -                                                                   |

| Branch: develop - New p                                          | header-stm32 submodule                                                       | device files.                                | Create new file Upload files                | Find file Clone or download ✓<br>Latest commit dd631c0 7 days ago<br>3 months ago               |

| Branch: develop   New p  Salkinium Update cmsis- devices         | header-stm32 submodule                                                       | device files.                                | Create new file Upload files                | Find file Clone or download ★<br>Latest commit dd631c0 7 days ago<br>3 months ago<br>7 days ago |

| Branch: develop   New p  Salkinium Update cmsis-  devices  tools | header-stm32 submodule<br>Update STM32 and AVR of<br>Update cmsis-header-str | device files.<br>m32 submodule               | Create new file Upload files                | Find file Clone or download -                                                                   |

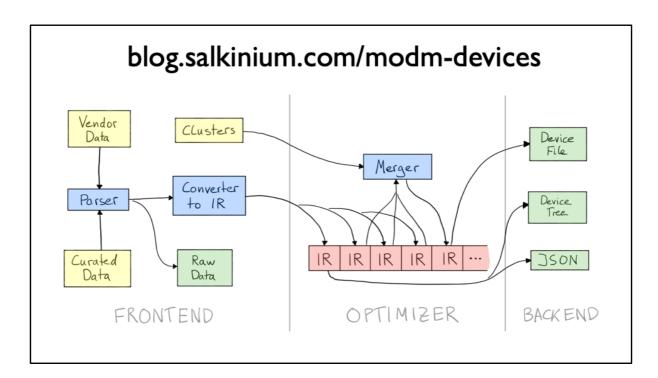

YOU can use this data too, it's on GitHub

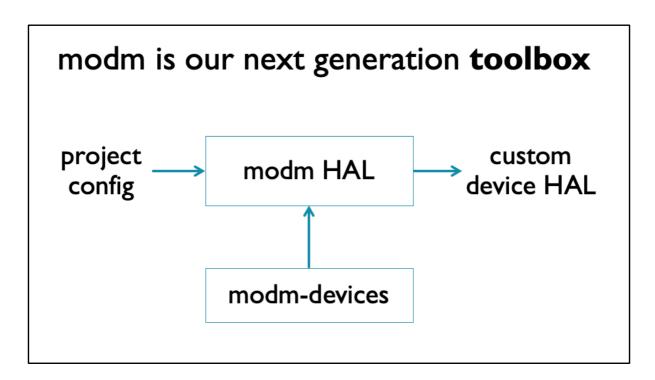

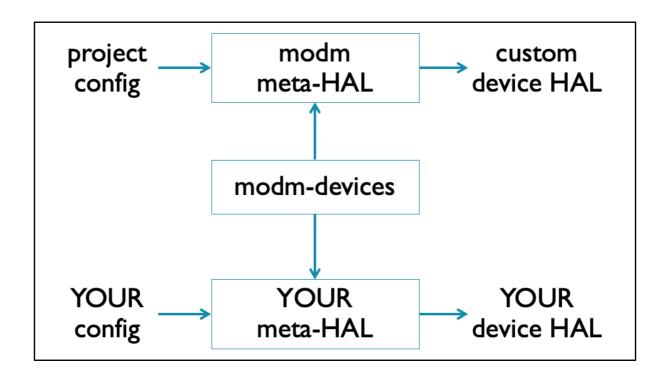

Fabian and I worked on modm for the last two years. It's a C++ HAL for STM32 and AVR. We use it to build the robot software for the Roboterclub Aachen.

modm is our INTERPRETATION of modm-devices.

It's a library GENERATOR, we specify a target id and it generates the HAL for us. We have ported ~80 AVRs and ~850 STM32 so far.

Share the data, not the HAL.

Easier to customize your HAL to your specific needs.

THIS IS LANGUAGE INDEPENDENT!

You generate C, Go, Rust, TEXT, you can also just generate documentation.

You can generate just ONE file, then gradually expand. Particularly useful to replace pain-points in existing code bases.

| Vertical vs. Horizontal Porting |         |              |            |              |          |  |  |  |  |  |  |

|---------------------------------|---------|--------------|------------|--------------|----------|--|--|--|--|--|--|

| Feature                         | STM32F0 | STM32FI      | STM32F3    | STM32F4      | STM32F   |  |  |  |  |  |  |

| Core                            | ✓       | $\checkmark$ | V          | $\checkmark$ | ~        |  |  |  |  |  |  |

| GPIO                            | ✓       | <b>√</b>     | V          | $\checkmark$ | V        |  |  |  |  |  |  |

| Clock                           | ✓       | <b>v</b>     | <b>v</b>   | <b>√</b>     | <b>v</b> |  |  |  |  |  |  |

| UART                            | ✓       | V            | V          | <b>√</b>     | <b>V</b> |  |  |  |  |  |  |

| SPI                             | VV      | VV           | <b>V</b> V | <b>V</b> V   | ×.       |  |  |  |  |  |  |

There is a change in how you port your targets now: Before: For each target implement the feature. Now: for each feature port to all targets

I glossed over the details of the actual code generation. You can read up on this on our website with examples. Installation guide, getting started guide, explanations how it works.

I'm not here to sell you on our HAL, I want to show you specific problems and how we used our toolbox to solve them.

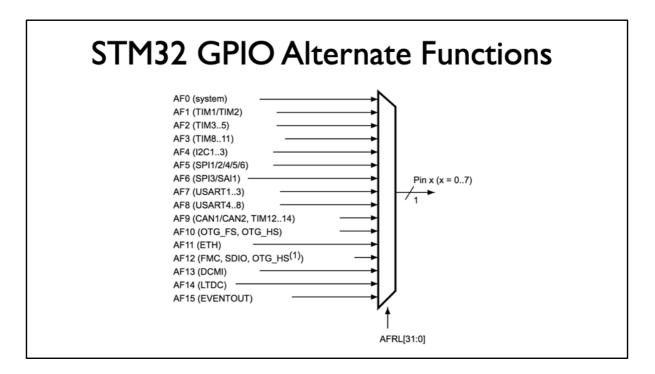

I've already touched on signal connections.

Each pin has a number of peripherals that it can be connected to.

|      |       |                |                       |              |                  |           |                      |                      |                           |                                |                                                |                                         |                                         |                          | 1                    |               |               |

|------|-------|----------------|-----------------------|--------------|------------------|-----------|----------------------|----------------------|---------------------------|--------------------------------|------------------------------------------------|-----------------------------------------|-----------------------------------------|--------------------------|----------------------|---------------|---------------|

|      |       | AF0            | AF1                   | AF2          | AF3              | AF4       | AF5                  | AF6                  | AF7                       | AF8                            | AF9                                            | AF10                                    | AF11                                    | AF12                     | AF13                 | AF14          | AF15          |

| Por  | Port  | SYS            | TIM1/2                | TIM3/4/<br>5 | TIM8/9/<br>10/11 | I2C1/2/3  | SPI1/2/3<br>/4/5/6   | SPI2/3/<br>SAI1      | SPI2/3/<br>USART<br>1/2/3 | USAR<br>T6/UA<br>RT4/5<br>/7/8 | CAN1/2/<br>TIM12/1<br>3/14/QU<br>ADSPI/L<br>CD | QUAD<br>SPI/OT<br>G2_HS<br>/OTG1<br>_FS | ETH                                     | FMC/SD<br>IO/OTG2<br>_FS | DCMI/<br>DSI<br>HOST | LCD           | SYS           |

|      | PA0   |                | TIM2_CH1/<br>TIM2_ETR | TIM5_CH1     | TIM8_ETR         |           |                      |                      | USART2_<br>CTS            | UART4_<br>TX                   |                                                |                                         | ETH_MII_CRS                             |                          |                      |               | EVENT<br>OUT  |

|      | PA1   | -              | TIM2_CH2              | TIM5_CH2     | -                | -         |                      | -                    | USART2_<br>RTS            | UART4_<br>RX                   | QUADSPI_<br>BK1_IO3                            | -                                       | ETH_MII_RX_<br>CLK/ETH_RMI<br>I_REF_CLK | -                        | -                    | LCD_R2        | EVENT<br>OUT  |

|      | PA2   | -              | TIM2_CH3              | TIM5_CH3     | TIM9_CH1         | -         | -                    | -                    | USART2_T<br>X             | -                              | •                                              | -                                       | ETH_MDIO                                | -                        | -                    | LCD_R1        | EVENT<br>OUT  |

|      | PA3   | -              | TIM2_CH4              | TIM5_CH4     | TIM9_CH2         | -         | •                    | -                    | USART2_<br>RX             | -                              | LCD_B2                                         | OTG_HS<br>_ULPI_D0                      | ETH_MILCOL                              | -                        | -                    | LCD_B5        | EVENT<br>OUT  |

|      | PA4   | -              | -                     | -            | -                | -         | SPI1_NSS             | SPI3_NSS/<br>I2S3_WS | USART2_<br>CK             | -                              |                                                | -                                       | -                                       | OTG_HS_S<br>OF           | DCMI_HS<br>YNC       | LCD_VSY<br>NC | EVENT<br>OUT  |

|      | PA5   | -              | TIM2_CH1/<br>TIM2_ETR |              | TIM8_CH1<br>N    | -         | SPI1_SCK             | -                    |                           | -                              |                                                | OTG_HS<br>_ULPI_C<br>K                  | -                                       |                          |                      | LCD_R4        | EVENT<br>OUT  |

|      | PA6   | -              | TIM1_BKIN             | TIM3_CH1     | TIM8_BKI<br>N    | -         | SPI1_<br>MISO        | -                    | -                         | -                              | TIM13_CH1                                      |                                         | -                                       |                          | DCMI_PIX<br>CLK      | LCD_G2        | EVENT<br>OUT  |

| Port | A PA7 | -              | TIM1_<br>CH1N         | TIM3_CH2     | TIM8_CH1<br>N    | -         | SPI1_<br>MOSI        | -                    | -                         | -                              | TIM14_CH1                                      | QUADSPI<br>_CLK                         | ETH_MII_RX_<br>DV/ETH_RMII<br>_CRS_DV   | FMC_SDN<br>WE            | -                    | -             | EVENT<br>OUT  |

|      | PA8   | MCO1           | TIM1_CH1              | -            | -                | I2C3_SCL  |                      | -                    | USART1_<br>CK             | -                              | •                                              | OTG_FS_<br>SOF                          | -                                       | -                        | -                    | LCD_R6        | EVENT<br>OUT  |

|      | PA9   | -              | TIM1_CH2              | -            | -                | I2C3_SMBA | SPI2_SCK/I<br>2S2_CK | -                    | USART1_T<br>X             | -                              | -                                              | -                                       | -                                       | -                        | DCMI_D0              | -             | EVENT<br>OUT  |

|      | PA10  | -              | TIM1_CH3              | -            | -                | -         | -                    | -                    | USART1_<br>RX             | -                              | -                                              | OTG_FS_<br>ID                           | -                                       | -                        | DCMI_D1              | -             | EVENT<br>OUT  |

|      | PA11  | -              | TIM1_CH4              | -            | -                | -         |                      | -                    | USART1_<br>CTS            | -                              | CAN1_RX                                        | OTG_FS_<br>DM                           |                                         | -                        |                      | LCD_R4        | EVENT<br>OUT  |

|      | PA12  | -              | TIM1_ETR              | -            | -                | -         |                      | -                    | USART1_<br>RTS            | -                              | CAN1_TX                                        | OTG_FS_<br>DP                           |                                         | -                        |                      | LCD_R5        | EVENT<br>OUT  |

|      | PA13  | JTMS-<br>SWDIO | -                     | -            | -                | -         | -                    | -                    | -                         | -                              |                                                | -                                       |                                         | -                        | -                    | -             | EVENT<br>OUT  |

|      | PA14  | JTCK-<br>SWCLK | -                     | -            | -                | -         | -                    | -                    | -                         | -                              | -                                              | -                                       | -                                       | -                        | -                    | -             | EVENT<br>OUT  |

|      | PA15  | JTDI           | TIM2_CH1/<br>TIM2_ETR | -            | -                |           | SPI1_NSS             | SPI3_NSS/<br>I2S3_WS | -                         | -                              | -                                              | -                                       | -                                       | -                        | -                    | -             | EVENT<br>'OUT |

These connections are hardcoded, and the possibilities are described in a very long table in the datasheet.

Several pages of tables.

You do NOT want to read through that.

# Gpio Signal Connection API GpioB7::connect(Uart1); GpioB6::connect(Uart1); But this code breaks RX on PB7! GpioB7::connect(Uart1); GpioA9::connect(Uart1);

We came up with this API. Just connect the pin to the peripheral.

Worked fine for a long time, until we ported to STM32F1! Things suddenly broke.

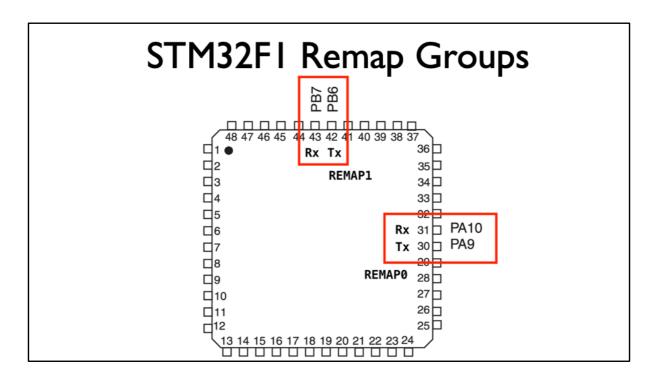

On the STM32F1 the GPIOs can only remap in groups. NO INDIVIDUAL REMAP POSSIBLE!

Our API has side-effects and the last call to set the group wins. This is an implicit assumption of our HAL API: Signal connections are independent of each other!

It's FALSE.

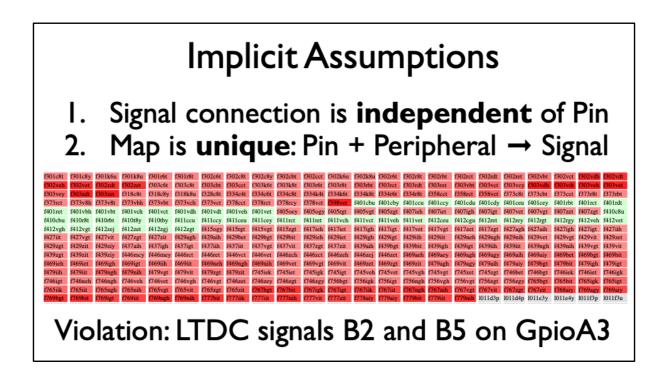

There is another assumption:

The combination of Pin NAME and Peripheral NAME is enough to \*\*uniquely\*\* identify the Signal connections.

So we wrote these assumptions as a test and ran it over all devices. Shows about 400 devices, the more red, the more violations.

An example violation: LCD display peripheral signals map two Blue signal lines onto the same pin.

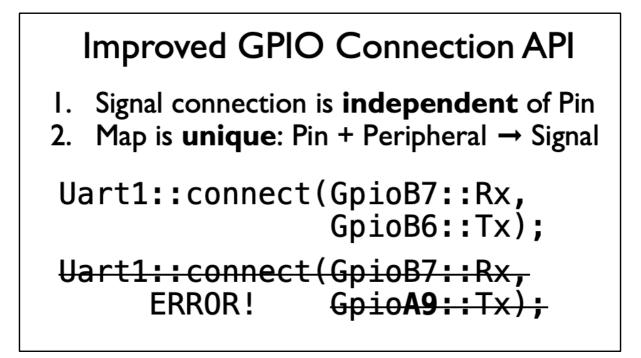

So we changed our API. Broke the entire code. And this API now remaps both in a group.

Compiler checks group remap validity.

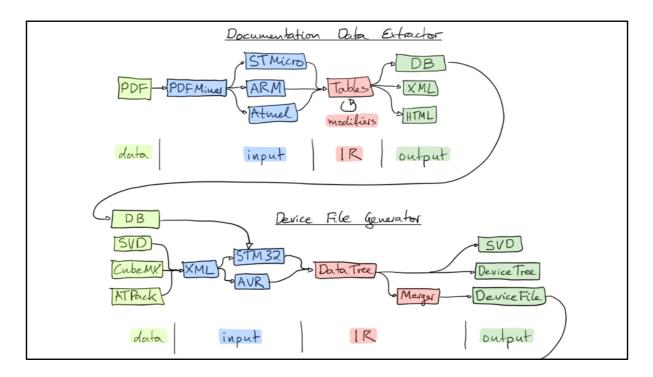

The CubeMX data doesn't contain everything we want. And it also doesn't scale to other vendors. So let's have a look at a very verbose data source: THE REFERENCE MANUALS.

| Let's parse some PDFs<br>Table 39. Summary of the DMA1 requests for each channel |                                                                                     |           |           |                 |                 |                 |                 |  |  |  |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------|-----------|-----------------|-----------------|-----------------|-----------------|--|--|--|

| Request.<br>number                                                               | - ' Channel 1   Channel 2   Channel 3   Channel 4   Channel 5   Channel 6   Channel |           |           |                 |                 |                 |                 |  |  |  |

| 0                                                                                | ADC1                                                                                | ADC2      | ADC3      | DFSDM1_<br>FLT0 | DFSDM1_<br>FLT1 | DFSDM1_<br>FLT2 | DFSDM1_<br>FLT3 |  |  |  |

| 1                                                                                | -                                                                                   | SPI1_RX   | SPI1_TX   | SPI2_RX         | SPI2_TX         | SAI2_A          | SAI2_B          |  |  |  |

| 2                                                                                | -                                                                                   | USART3_TX | USART3_RX | USART1_TX       | USART1_RX       | USART2_RX       | USART2_TX       |  |  |  |

| 3                                                                                | -                                                                                   | I2C3_TX   | I2C3_RX   | I2C2_TX         | I2C2_RX         | I2C1_TX         | I2C1_RX         |  |  |  |

This is a DMA channel to peripheral mapping.

This is data that's not available in the CubeMX dataset.

We need it anyways to provide a channel connection API.

| PDF X-Ray Vision   |           |           |           |                  |                 |                  |                  |  |  |  |  |

|--------------------|-----------|-----------|-----------|------------------|-----------------|------------------|------------------|--|--|--|--|

| Reguest.<br>number | Channel 1 | Channel 2 | Channel 3 | Channel 4        | Channel 5       | Channel 6        | Channel 7        |  |  |  |  |

| ٥                  | ADC1      | ADC2      | ADC3      | DESDM1_<br>FLITO | DESDM1_<br>ELTI | DESDM1_<br>FLIT2 | DESDM1_<br>ELIT3 |  |  |  |  |

| đ                  | -         | SPI1_RX   | SPI1_IIX  | SPI2_RX          | SPI2_TIX        | SAI2_A           | SAI2_B           |  |  |  |  |

| 2                  | -         | USART3_TX | USART3_RX | USARTI1_TIX      | USARTI1_RX      | USART2_RX        | USART2_TX        |  |  |  |  |

| 3                  | -         | I2C3_IIX  | I2C3_RX   | 12C2_TX          | 12C2_RX         | 12C1_TX          | I2C1_RX          |  |  |  |  |

I wrote a program to give me X-Ray vision of the PDF. Read the Adobe PDF specification, it's quite fun.

PDF is a print format, it does not contain any semantical intofmraiton. This is not a table. It is a bunch of lines and a bunch of text overlaid.

You can recognize tables fairly easily, and then translate their contents.

# Table extraction is doable

| Re-<br>quest.<br>num-<br>ber | Chan<br>nel 1 | Channel<br>2   | Channel<br>3   | Channel 4        | Channel 5        | Channel 6        | Channel<br>7     |

|------------------------------|---------------|----------------|----------------|------------------|------------------|------------------|------------------|

| 0                            | ADC1          | ADC2           | ADC3           | DFSD-<br>M1_FLT0 | DFSD-<br>M1_FLT1 | DFSD-<br>M1_FLT2 | DFSD-<br>M1_FLT3 |

| 1                            | -             | SPI1_RX        | SPI1_TX        | SPI2_RX          | SPI2_TX          | SAI2_A           | SAI2_B           |

| 2                            | -             | USAR-<br>T3_TX | USAR-<br>T3_RX | USART1_T<br>X    | USART1_R<br>X    | USART2_R<br>X    | USART2_T<br>X    |

| 3                            | -             | I2C3_TX        | I2C3_RX        | I2C2_TX          | I2C2_RX          | I2C1_TX          | I2C1_RX          |

|                              |               |                |                |                  |                  |                  |                  |

### Understanding descriptions is very hard

This is a prototype extraction. Tables are structured information by definition. So it's somewhat easy to extract and use this data.

However, the textual descriptions of periphrals are very hard to turn into some kind of structured information.

The difficulty is not the table extraction it's the data cleanup and simplification. You need to condense this information into something that easily usable for the developer.

There are hundreds of these datasheets + reference manuals. This isn't easy.

There are bugs in them, sometimes types in register names, sometimes worse. It's going to be difficult to get some ground truth out of this.

ST also produces SENSORS, which also have Datasheets. They have the same formatting as the reference manuals, so you can just extract tables in there too.

And so we can build a database of sensors as well. They are always the same: Memory Mapped IO via SPI/I2C.

They are by definition already platform-independent. So why aren't there COMMON drivers for all platforms? Abstract description of the protocol

This is really self-explanatory.

This is how I envision the future of Porting Embedded Software to hundreds of devices.

We parse ALL of the datasheets, THEN MAGIC, THEN PROFIT.

## Thank you for listening!

Niklas Hauser: @salkinium (GitHub/Twitter) (blog.)salkinium.com

> modm.io github.com/modm-io

EY MANN, WO IS' MEIN TSCHUNK?